当前位置: 主页 > 资讯中心 > 技术资料 » TMS320C6657CZHA25数字信号处理器和控制器-技术资料

TMS320C6657CZHA25

| 品牌: | TI |

| 型号: | TMS320C6657CZHA25 |

| 数量: | 914 |

| 制造商: | Texas Instruments |

| 产品种类: | 数字信号处理器和控制器 - DSP, DSC |

| RoHS: | 是 |

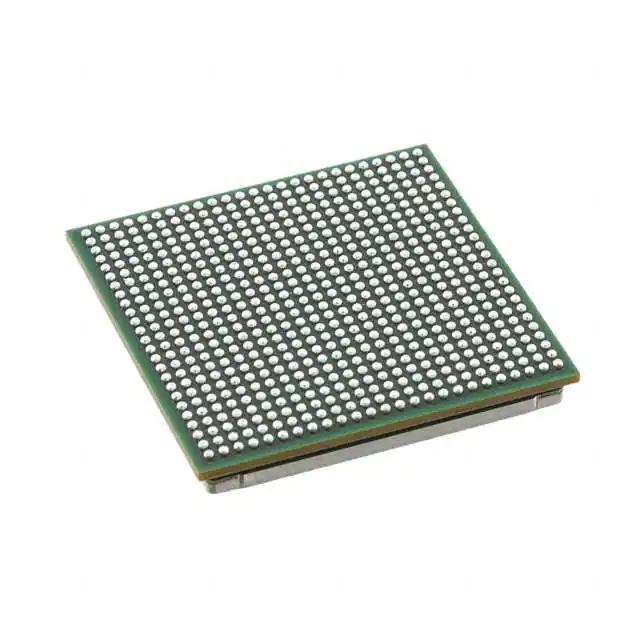

| 安装风格: | SMD/SMT |

| 封装 / 箱体: | FCBGA-625 |

| 系列: | TMS320C6657 |

| 核心: | C66x |

| 最大时钟频率: | 1 GHz, 1.25 GHz |

| 程序存储器大小: | 128 kB |

| 数据 RAM 大小: | 3 MB |

| 工作电源电压: | 900 mV to 1.1 V |

| 最小工作温度: | - 40 C |

| 最大工作温度: | + 100 C |

| 程序存储器类型: | SRAM |

| 数据 ROM 大小: | 128 kB |

| 接口类型: | EMAC, I2C, Hyperlink, PCIe, RapidIO, UPP |

| MMACS: | 80000 MMACS |

| 湿度敏感性: | Yes |

| 计时器/计数器数量: | 10 Timer |

| 电源电压-最大: | 1.1 V |

| 电源电压-最小: | 900 mV |

| 单位重量: | 4.886 g |

C665x是基于Tl的KeyStone多体系结构的高性能固定和浮点DSP。结合了创新的C66xDSP核心,该设备可以以高达1.25GHz的核心速度运行。对于广泛应用的开发人员来说,这两款C665x DSP都提供了一个节能且易于使用的平台。此外,C665x DSP与现有的C6000r系列固定和浮点DSP完全向后兼容。TI的KeyStone体系结构提供了一个可编程平台,集成了各种子系统(C66x核心存储器子系统、外围设备和加速器),并使用了一些创新的组件和技术来最大限度地提高设备内和设备间的通信,使各种DSP资源能够高效无缝地运行。该体系结构的核心是诸如MulticoreNavigator之类的关键组件,其允许在各种设备组件之间进行高效的数据管理。TeraNet是一种非阻塞式交换机结构,可实现快速且无争用的内部数据移动。多刷新共享内存控制器允许直接访问共享内存和外部内存,而无需从交换机结构中提取容量。

对于定点使用,C66x内核的乘法累加(MAC)能力是C64x+内核的4倍。此外,C66x核心集成了浮点功能,每个核心的原始计算性能是业界领先的每个核心40 GMACS和每个核心20 GFLOPS(工作频率为1.25 GHz)。C66x内核每周期可执行8次单精度浮点MAC操作,可执行双精度和混合精度操作,符合IEEE 754标准。C66x内核包含90条新指令(与C64x+内核相比),用于浮点和矢量数学处理。这些增强在信号处理、数学和图像采集功能中使用的流行DSpkernel中产生了相当大的性能改进。C66x内核与Tl的上一代C6000固定和浮点DSP内核向后兼容。确保了软件的可移植性,并缩短了向主硬件迁移的应用程序的软件开发周期。

C665x DSP集成了大量的片上存储器。除了32KB的L1程序和数据缓存外,1024KB的专用内存可以配置为映射RAM或缓存。该设备还集成了1024KB的多核共享存储器,可以用作共享L2 SRAM和/或共享L3SRAM。所有L2存储器都包含错误检测和错误校正。为了快速访问外部存储器,该设备包括一个以1333MHz的速率运行的32位DDR-3外部存储器接口(EMIF),并支持ECC DRAM。

该系列支持许多高速标准接口,包括RapidlO ver2、PCI ExpressGen2和千兆以太网。该系列DSP还包括1C、UART、多通道缓冲串行端口(McBSP)、通用并行端口(uPP)、16位异步EMIF以及通用CMOS I0.对于设备之间或与FPGA之间的高吞吐量、低延迟通信,包括一个称为HyperLink的40Gbaud全双工接口。

C665x设备有一套完整的开发工具,其中包括:一个增强的C compileran汇编优化器,用于简化编程和调度,以及一个Windows@调试器接口,可用于源代码执行。

TI的KeyStone多核体系结构提供了一种高性能结构,用于将RISC和DSP核与特定应用的协处理器和/0集成。KeyStone架构是同类架构中第一个为处理核心、外围处理器的非阻塞访问提供足够内部带宽的架构。和1/0.这种内部带宽是通过四个主要硬件元件实现的:多核心导航器、TeraNet、多核心共享内存控制器和HyperLink。

多核导航器是一种创新的基于数据包的管理器,可控制8192个队列。将任务分配给队列时。多核导航器提供硬件加速调度,将任务定向到适当的可用硬件。基于分组的片上系统(SoC)使用TeraNet交换中心资源的两个Tbps容量来移动分组。多核共享内存控制器允许处理核直接访问共享内存,而无需从TeraNet的容量中提取,因此数据包移动不会被内存访问阻止

HyperLink提供40 Gbaud芯片级互连,使SoC能够串联工作。Hyperlink的低协议头和高吞吐量为芯片间互连提供了理想的接口。使用多核导航器,Hyperlink可以透明地将任务分派到串联设备,并像在本地资源上运行一样执行任务。